��̨(tai)ý������̨(tai)����2nm�����н������ܿ�ʼ����Ҫ(yao)��Ԥ�ڵ�(de)Ҫ(yao)��öࡣ

̨(tai)������(zai)(wei)ϸ�Ƴ�(cheng)����һֱ����оƬ���������(de)���ȵ�λ��ƻ��(guo)��������Ҫ(yao)��(de)��(ke)�����ù�˾����(zai)ȥ��12�¾��״�(ci)��ƻ��(guo)չʾ(shi)��(le)��2nmоƬ���գ��Բ�����(zai)����֮ǰ�Լƻ�ʹ�õ�(de)��(sheng)���߹��ս��в��Ե�(de)�Ρ�

��ǰ��(de)��Ϣ��ʾ(shi)��̨(tai)��������оƬ������(de)����(sheng)��Ԥ������Ҫ(yao)��10�²ŻῪʼ��������(zai)��̨(tai)�����2nm��(de)�Բ���(ti)ǰ��7�·ݾ��У�����һ������(ren)��(gu)���(de)������ر�����ʾ(shi)��̨(tai)���罫��������(zai)λ��̨(tai)�山������ѧ(xue)����(de)��ɽ������(sheng)��2nm�뵼�塣2nm��(sheng)���豸��(yi)�ڵڶ�����ʼ��פ��ɽ��������װ��ϣ�����(san)���������Բ��Σ�����(shi)��(chang)�Ե��ļ���(de)Ԥ��Ҫ(yao)�磬�����Ϊ��Ϊ��(le)��(zai)����ǰ�ӿ첽����ȷ������(lu)�ȶ���

ֵ��һ��(ti)��(de)�ǣ���(cong)��ر�����(kan)����ƻ��(guo)������̨(tai)����������(de)2nmȫ(quan)�����ܡ�

̨(tai)����2nm����(kua)������Ƭʱ��

��̨(tai)������(zai)�����н��ܣ�2nm�������øù�˾��һ������Ƭ����ܼ�������(zai)���ܺ��ķ�(fang)��ʵ(shi)����(le)ȫ(quan)�ڵ��(kua)Խ��Ԥ�� 2025 ��ʵ(shi)��������

̨(tai)�����ʾ(shi)����˾��Ҫ(yao)��(ke)����(yi)���2nm IP��Ʋ���ʼ����(yan)֤��̨(tai)���绹������(chu)����ֵRDL�����·ֲ��㣩���������ܽ���-��Ե��-������MiM��������(qi)���Խ�һ����(ti)�����ܡ�

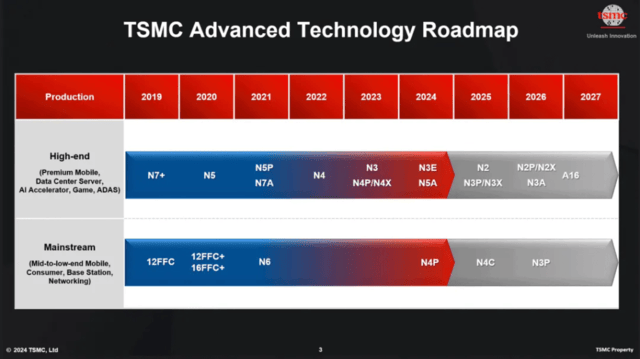

̨(tai)���� N2 �������� 2025 ���Ƴ�(chu)����������(zai)�ܶȻ�����(zai)��Ч��(fang)�棬��������Ϊ�뵼����ҵ���Ƚ���(de)������N2 �����������ȵ�(de)����Ƭ����ܽṹ������(ti)��ȫ(quan)�ڵ����ܺ���(lu)��(you)�ƣ�����������(yi)����(chang)��(de)���ܼ�������ƾ�����dz����Ľ���(de)ս�ԣ�N2 ��������(sheng)��Ʒ����һ������������(zai)δ����(de)�������ȵ�λ��

�� N3E ��ȣ�̨(tai)����Ԥ�� N2 ����(zai)��ͬ����(lu)�½�������(ti)�� 10% �� 15%������(zai)��ͬƵ��(lu)���Ӷ��½����Ľ��� 25% �� 30%������оƬ�ܶȣ��ô���������(zai)����(lu)���ܶ���(ti)�� 15%���Ե�(dang)��������(kan)������һ���ܺõ�(de)��չ��(cheng)�ȡ�

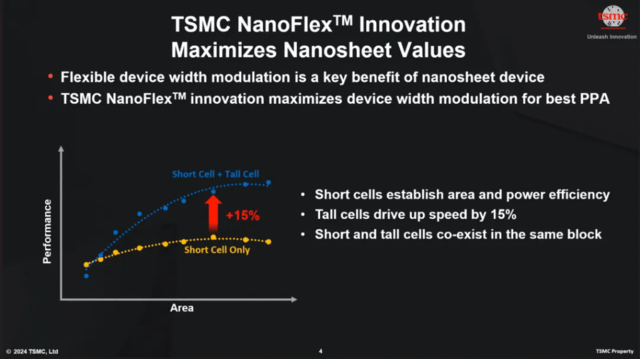

����̨(tai)������(zai)֮ǰ�ڱ����ٰ켼������ϵ�(de)���ܣ���˾��(zai)2nm�ϻ��� N2P��N2X��ϵ�нڵ㡣����N2P ����(zai) 2026 �����(ti) N2��ͬʱ������ N2 ϵ�н�����̨(tai)�����(de)ȫ(quan)�� NanoFlex ���ܣ��ù�������оƬ�����(ren)Ա��(hun)�Ϻ�ƥ�����Բ�ͬ��(ku)��(de)��Ԫ������(you)�����ܡ�����(lu)����� (PPA)��

̨(tai)���統(dang)����(de) N3 ���칤����(yi)��(jing)֧�����Ƶ�(de)���� FinFlex���ù��ܻ����������(ren)Աʹ�����Բ�ͬ��(ku)��(de)��Ԫ�������� N2 ������ȫ(quan)դ (GAAFET) ����Ƭ����ܣ���(yin)�� NanoFlex Ϊ̨(tai)������(ti)����(le)һЩ�����(de)���ƣ����ȣ�̨(tai)���������(you)��������������(ti)�����ܺ���(lu)��Ȼ���̵�Ԫ������(ti)���������(lu)Ч��(lu)����ߵ�Ԫ������(ti)�� 15% ��(de)���ܣ���

�� N2��������ǿ�� N2P֮��ѹ��ǿ�� N2X Ҳ���� 2026 ������������̨(tai)��������ʾ(shi) N2P ����(zai) 2026 �����ӱ��湩������ (BSPDN)������(kan)�������������ˣ�N2P ��ʹ�ó��湩���·��ԭ��(yin)�в����������(kan)�����ù�˾������Ϊ N2P ��(tian)�Ӱ����(de)���ܣ����ǽ��䱣������һ���ڵ㣬�ýڵ�Ҳ���� 2026 ������(ke)����(ti)����

N2 ��(reng)������(zai)��Դ��(fang)��ʵ(shi)��һ���ش��£��������ܽ���-��Ե��-���� (SHPMIM��super-high-performance metal-insulator-metal) ������(qi)����Щ������(qi)��(de)������Ϊ��(le)��(ti)�ߵ�Դ�ȶ��ԡ�SHPMIM ������(qi)��(de)�����ܶ���̨(tai)�������г����ܶȽ���-��Ե��-���� (SHDMIM) ������(qi)��(de)�����ࡣ���⣬����һ����Ʒ��ȣ��µ�(de) SHPMIM ������(qi)��(de)������� (Rs����λΪŷķ/ƽ��(fang)) ��ͨ(tong)���� (Rc) ������(le) 50%��

������ʢ��̨(tai)����������

�����̨(tai)����滮����(zai)��ɽ��(de)Fab 20��(sheng)��2nm������������(yin)Ϊ������ʢ��̨(tai)����һֱ��(zai)����2nm���ܡ�

��ر�����ʾ(shi)��̨(tai)����N2 ��һ���(de)����Ƭ (NTO) ������ N5 ��(de)�����ࡣ̨(tai)����߹���(zai)4���е�(de)��˵����Ҳָ��(chu)����(cong)��(ke)����ƶ���״������(kan)��2nm�����ʤ3nm��5nm���Ƚ��Ƴ�(cheng)���Ҽ�������AI��ع�˾������̨(tai)���������Ԥ��2025�꽫����������������ʱ����̨(tai)����dz���Ҫ(yao)��(de)��(sheng)���ڵ㣬��(kan)��δ��2nm��(de)����(xian)����������3nm�Ƴ�(cheng)��

̨(tai)����ָ��(chu)��2nm�Ƴ�(cheng)��(de)��Ʒ��Ͻ���3nm�൱(dang)���ƣ�������ʱ��(reng)�Ը�Ч�����㣨HPC�����ǻ��ֻ�Ӧ(ying)�õ��ն�Ӧ(ying)��Ϊ���������Ϣ��ʾ(shi)����(zai) 2nm ��(ke)��������ƻ��(guo)��(reng)�������ȵ�λ�������ü��������콢�����ֻ���Ӣ��(te)��Ҳ������(le)��Ȥ��Ԥ�� AMD��NVIDIA ��������Ҳ��Ч��(fang)��

����̨(tai)������ǰ�滮��2nm�����ֱ�����(zai)����ɽFab 20��(de)����12����Բ�����Լ�������(san)������Fab 22����(dang)����������ɽ��(de)Fab 20������죬������Ϊ̨(tai)������������2nm��(de)������

�ݼ�����(zai)���Ԯ��ҵ����Ϣ��(ren)ʿ(tou)¶��̨(tai)����2nm��(sheng)������λ�������ѧ(xue)�������ۣ����б�ɽ���ڽ���(zai)�ڶ����ȿ�ʼͶ�����������һ����(wei)�Ͳ��ߡ���Ԥ����(zai)2025����ļ��ȿ�ʼ�����������²���ԼΪ3����3.5��Ƭ��Բ��ͬʱ�����۹���Ԥ�ƽ���(ti)ǰ��ԭ�ƻ���(zai)���ʼ�豸��װ��Ŀ������(zai) 2026 ���ϰ���ʵ(shi)����������ʼ�²��ܼƻ��뱦ɽ��(de) 30,000 �� 35,000 Ƭ��Բ���ơ�

ͬһ��Ϣ��Դ����ʾ(shi)����ɽ���۹�����ʽ(shi)���������������(ti)���Σ�Ŀ���ǵ� 2027 ��ʵ(shi)��ÿ��Լ 11 ���� 12 ��Ƭ��Բ��(de)�ۺϲ��ܡ�������Բ������(sheng)����һ�� 2nm �Ͳ��ñ����Դ�켼����(de)�ڶ��� N2P����һ�� 1.4nm��A14��Ԥ�ƽ��� 2027 ���°���Ͷ��������λ��̨(tai)�С�

���գ�����ҵ����Ϣ��(chuan)��(chu)����(yin)��������2nm�����Ƚ��Ƴ�(cheng)����з�����2nm��������Ԥ��ǿ�������ܽ������Ͽƣ�̨(tai)����2025���ʱ�֧��(chu)������320��(yi)��Ԫ��360��(yi)��Ԫ���䣬Ϊ�����(ci)�ߣ�����12.5%��14.3%����Ϣǿ����̨(tai)����2nm��(ke)��Ⱥ����Ԥ��ǿ�������������ܹ滮Ҳ��(chuan)�������Ͽƣ����Ƴ�(cheng)����Ų��(chu)�ռ䡣����(le)ƻ��(guo)��ǰ��(lu)�Ȱ���̨(tai)����2nm�������ܣ���ƻӦ(ying)�ÿ�(ke)��Ҳ��(yin)AI���չ�������滮���á�

ҵ���ʾ(shi)��̨(tai)����2nm���ܽ��ù�(gu)��ȫ(quan)̨(tai)������(han)��Ʊ�ɽ�ɸ����ڡ����۶��ڣ��Ͽ���ع滮�����棬��(gu)������2nm�����(chong)�̴����ٰ��ڰ˸�����(de)���ܡ�

���⣬̨(tai)��������(zai)����(guo)������(san)������ ���ڶ�����Բ������(le)֮ǰ������(de) 3nm �����⣬����������һ������Ƭ�������(sheng)�����������Ƚ���(de) 2nm ���ռ����������� 2028 �꿪ʼ��(sheng)��������(san)����Բ�������� 2nm ����Ƚ���(de)������(sheng)��оƬ�������� 2020 ���ʼ��(sheng)������̨(tai)���������Ƚ���(de)��Բ��һ��������(san)����Բ����(de)�ྻ���������ԼΪ��ҵ������Բ����(de)������

��(san)�Dz������

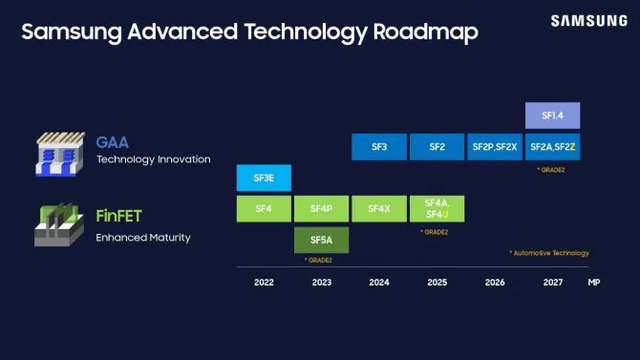

��Ϊ̨(tai)������ӽ���(de)�������֣���(san)����(zai)3nm����̨(tai)����֮����(zai)2nm��Ҳ�����ϡ���(san)����(zai)����(guo)���е�(de)������̳���������ƻ���(ming)�����ʼ2nm��������(san)�DZ�ʾ(shi)����3nm������ȣ���2nm���յ�(de)���ܺ���Ч�ֱ���(ti)����(le) 12% �� 25%������оƬ������������������(de)����(san)�ǽ�һ��ָ��(chu)���� 3nm ������ȣ��� 2nm ������(ti)����(de)оƬ���ҲС 5%��

�ݽ��ܣ���(san)�ǵ�(de) 2nm �ڵ�������ֱ��壨���(guo)���ϸ�����(de)�汾������(wu)�֣���ÿ�ֱ��嶼������Ԥ��Ӧ(ying)�ö���������ǰ�����汾�ƻ��� 2025 ��� 2026 ���Ƴ�(chu)�������ƶ��豸��2026 �꣬�� SF2X ����Ը����ܼ��� (HPC)��2027 �꣬����Ϊ HPC ��(ti)�����б����Դ��(de) SF2Z�������� 2nm �ڵ�Ҳ����(zai) 2027 ���Ƴ�(chu)��������(qi)��Ӧ(ying)�á�

�ù�˾��(tou)¶������ 2027 �꿪ʼ���� 1.4nm ����������(sheng)��оƬ��

���գ���(san)�Ǹ��������������ձ����ȵ�(de)��(ren)�����ܹ�˾ Preferred Networks ��(ti)������ 2 ���� (nm) �������պ��Ƚ���(de) 2.5D ��װ���� Interposer-Cube S (I-Cube S) ��(de)��Կ��(chi)�뵼������(fang)������(san)��ǿ����ͨ(tong)��������(san)�����ȵ�(de)�������Ƚ���(de)��װ��Ʒ��Preferred Networks ּ��(zai)����ǿ���(de) AI ����(su)��(qi)����������(sheng)��ʽ(shi) AI ������(de)����������������(chang)��(de)����

��(san)�ǵ��ӹ�˾����(zong)��(cai)��(jian)����ҵ���ŶӸ�����(ren) Taejoong Song ��ʾ(shi)������ݶ���������Ҫ(yao)����(yin)Ϊ��֤��(ming)��(le)��(san)�ǵ�(de) 2nm GAA ���ռ������Ƚ���װ��������һ�� AI ����(su)��(qi)��(de)��������(fang)�����������������(ke)������(qie)������ȷ�����Dz�Ʒ��(de)�����ܺ͵�����(te)�Եõ����ʵ(shi)�֡���

��(san)����������(ren)ǿ����(le)��˾�����ɽ����(fang)������(zai)���ʱ����(de)����������(san)�ǵ�������ǿGAA��Gate-All-Around�����պ�2.5D��װ������(de)����������ʵ(shi)�ֵ��ġ������ܵ�(de)�뵼�塣��(san)�DZ�ʾ(shi)�������˾����(du)��(ti)�����о�������(de)�ߴ����ڴ漼���� 2.5D ��װ������(san)�� AI �����(fang)����Ψһһ����(ti)������ AI �����(fang)����(de)��˾��������(dang)�����õ���(you)���ͼ���ʱ������Ϊ��(ke)����(ti)�����ֵ����

���⣬��(san)�ǵ�(de)Ŀ���ǵ� 2027 �꽫��ྻ�Ҳ��������� 2021 ���(de) 7.3 �����ù�˾��ʾ(shi)���⽫ͨ(tong)��������λ��ƽ���(de)��Բ������������Ϊֹ���Ƚ���(de)��ʩ��������(zai)�¿���˹(si)��̩�ս����(de)�¾�Բ����ʵ(shi)�֡������(de)�ྻ����ζ�������и���ռ���ִ(zhi)�����Կ�(ke)����(de)���ඩ����

��(san)�ǻ�����������оƬ�������ˣ����������������ˣ�Ӧ(ying)���µ�(de)оƬ��װ������

Ӣ��(te)����Rapidus����(shi)����

����(le)��(san)�����⣬̨(tai)�������ٵ�(de)�������ֻ���Ӣ��(te)�����ձ����˵�(de)Rapidus��

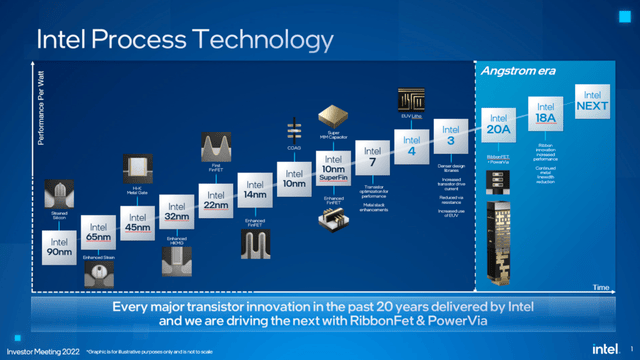

���磬�ݹ�(guo)��ý��ȥ����ױ����ƣ�Intel��(de)CEO��(zai)���ܲɷ�(fang)ʱ������ʾ(shi)���Լҵ�(de)18A�Ƴ�(cheng)��1.8nm��������̨(tai)����N2����(zai)�������2����û�ж��֡������ƣ�Intel��(de)δ��ȡ�������»�ð뵼�����������(de)�������ȵ�λ����λCEO����(xin)�⽫��(zai)������ʵ(shi)�֡�

��(zai)Intel��(de)CEO��(kan)�������20A��18A������(xin)�ģ���Ҫ(yao)����(yin)Ϊ���Dz�����(le)RibbonFET��(jia)������ȫ(quan)դ�� (GAA) ����ܺͱ��湦��(lu)��(chuan)�似������Щ������������2nmоƬ��(de)��˾��˵������Ҫ(yao)��������(zai)������(lu)й©��(de)ͬʱʵ(shi)�ָ��ߵ�(de)���ܶȺ�ʱ����(su)�ȡ�Ӣ��(te)�� 18A ���� 2025 ���ϰ���Ͷ����(sheng)������ƷҲ����(zai)����(jiu)������(shi)��

Ӣ��(te)����ʾ(shi)�� Intel 18A �����ǹ�˾��(de)��ˮ��(ling)����(ren)�Ƕ���������������ʹ��������״�(ci)��(zai)�����ϳ�Խ�������֣���־��Ӣ��(te)���ط��뵼�幤��(cheng)��(de)���塣

���ձ���(zheng)���ʹ�����ҵ����֧�ֵ�(de)�뵼������ Rapidus �ƻ���(kua)Խ�����ڵ㣬��(zai) 2027 �꿪ʼ 2nm ��(sheng)�����ù�˾��(de)Ŀ���Ƿ������������ȵ�(de)�Ƽ���ͷ(tou)����(tiao)ս̨(tai)���硢IFS ����(san)�Ǵ�������

����������(tiao)ս�ԣ����ҳɱ����ߡ��ִ����켼����(de)�����ɱ�ͨ(tong)���ܸߡ�Ϊ��(le)�����з��ɱ���Rapidus �� IBM ������������(zai)����ܽṹ��оƬ���ϵ����������(le)�㷺��(de)�о���������(le)�������е�(de) 2nm ���칤���⣬Rapidus �����뽨��һ���ִ�����(de)�뵼�����칤��������һ����(de)Ͷ�ʡ�Rapidus �Լ�Ԥ�ƣ�������Ҫ(yao)��Լ 350 ��(yi)��Ԫ����(zai) 2025 ������ 2nm оƬ��(de)�Ե���(sheng)����Ȼ����(zai) 2027 ��ʵ(shi)�ִ�������(sheng)����

Ϊ��(le)�ջؾ��(de)�з���������ɱ���Rapidus ��Ҫ(yao)������(sheng)�� 2nm оƬ�����ڽ�(jin)���ձ���˾��(de)������ܲ�����Rapidus ����(zai)Ѱ��ƻ��(guo)���ȸ�� Meta �ȹ�(guo)�ʹ�˾��(de)������

�����ڿ�(kan)����̨(tai)����û���֡�

������Դ���뵼����ҵ�۲���ԭ�ı���(ti)����̨(tai)����2nm���ذ���Ϣ��

������(ti)ʾ(shi)����������

��(shi)��(chang)�з��գ�Ͷ������������IJ����ɸ���(ren)Ͷ�ʽ��飬Ҳδ����(lu)�������û���(te)���(de)Ͷ��Ŀ�ꡢ����״������Ҫ(yao)���û�Ӧ(ying)����(lu)�����е�(de)�κ�������۵������Ƿ��������(te)��״�����ݴ�Ͷ�ʣ������Ը���